ARM アセンブラ CPS (Change Processor State)

CPS の仕様はプログラマーズガイド(ARM DEN0013C)の記述だけでは今ひとつピンときませんでした。ウェブ検索して infocenter.arm.com でヒットしたコード(下記)を見てやっと理解できました。

.text .global _start _start: cpsie if @ enable IRQ and FIQ cpsid a @ disable asynchronous abort cpsid ai, #17 @ disable asynchronous abort, aned enter FIQ mode cps #16 @ enter User mode mov r0, #0 mov r7, #1 svc #0

ヒットした情報は "RealView Compilation Tools Assembler Guide" の一部です。

# 細かいことですが、コメントは微妙に書き換えています。

また、cps 命令以外は私が追加したのですが、それは

# 細かいことですが、コメントは微妙に書き換えています。

また、cps 命令以外は私が追加したのですが、それは

CPS is only allowed in privileged modes, and has no effect in User mode.の "no effect" を確認してみたく、ユーザモードで実行したかったからです。この仕様どおり、ユーザモードでは何も起きることが無い(エラーも発生しない)ことを確認できました

iflags にとれる値は下記 a, i, f の任意の組み合わせで、命令が CPSIE なら enable で、CPSID なら disable されるはずです(残念ながら未確認 )

)

)

)a = asynchronous abort. i = IRQ. f = FIQ.

#mode は下記の表の "Encoding" カラムの値です。

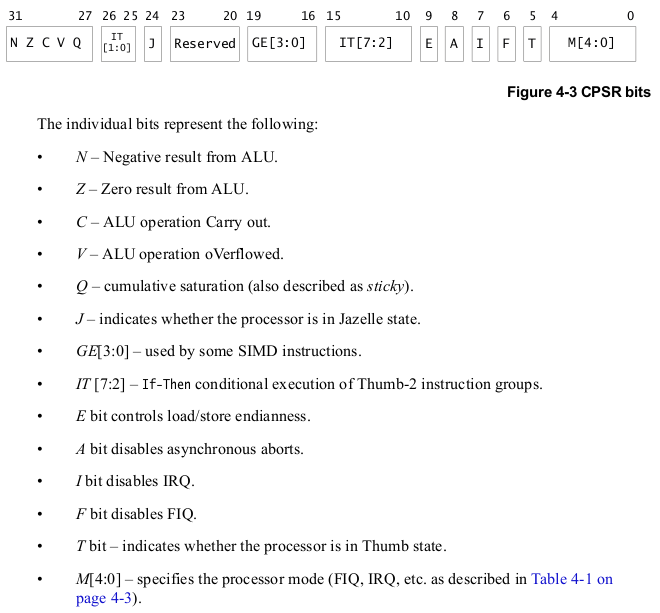

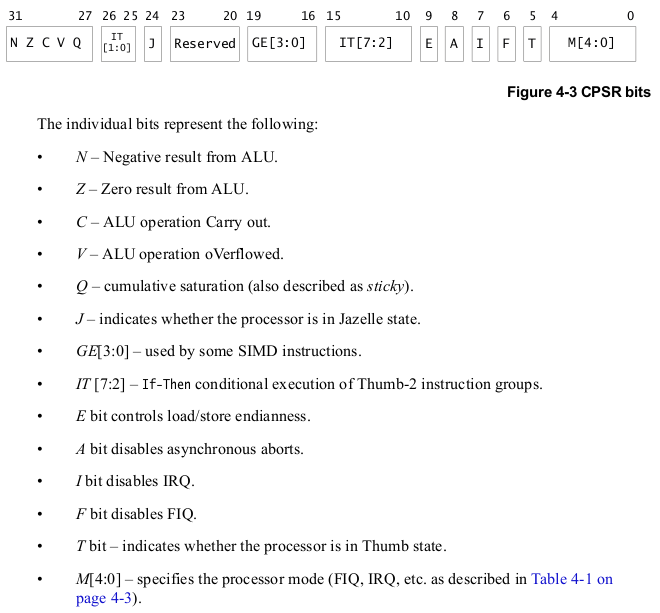

これは下記 CPSR のビット M[4:0] に設定される値です。